# ΤΕΜΙΟ

#### MATRA MHS

# **Multi-Channel HDLC Protocol Controller**

# Description

The MHS 29C94 is a multi channel data link protocol controller device. It multiplexes/demultiplexes up to 32 full duplex data channels to support implementation of high speed data links based on either HDLC protocol or clear channel.

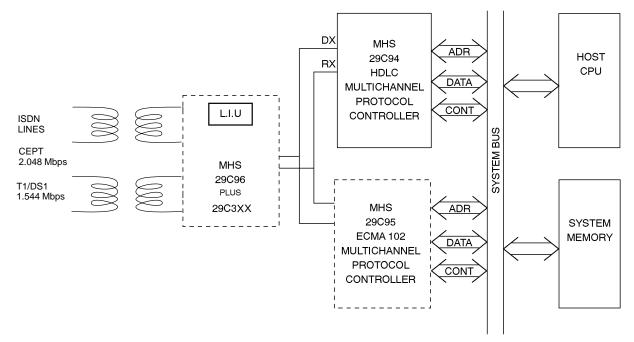

The device operates at layer 2 of the OSI (Open System Interconnection) model as described by ISO (International Organization for Standardization). It resides between a L.I.U. and a framer PCM devices such as, respectively, the MHS 29C3XX and 29C96, and a memory shared with a system host microprocessor.

The 29C94 processes transmit and receive data on a PCM communication medium in either the CEPT (2.048 Mbps) or the T1/DS1 (1.54 Mbps) framing format. The device provides HDLC formatting/ extract functions for synchronous data and manages, for each of the active data channels, access to buffers into the shared memory.

Provisions to operate in clear channel, non-HDLC mode, are readily available and can be programmed on any channel independently of every others.

# Features

- Single chip CMOS monolithic device simplifies ISDN/DMI implementation

- Compatible with 2.048 Mbps CEPT and 1.544 Mbps T1/DS1 PCM framing format.

- Provides HDLC or clear channel formatting for up to 32 full duplex, 64 kbps channels.

- On chip receive and transmit context saving as well as buffer memory management function.

- Provides 64 DMA channels (32 transmit, 32 receive), 8-bit data bus, 24-bit address, bus request/acknowledge, handshake

- Provides any user defined hyperchannel and ISDN standard hyperchannel options (CCITT I.412), - H<sub>0</sub> (384 kbps),

- $H_{11}$  (1.536 Mbps),

- H<sub>12</sub> (1.920 Mbps).

# Interface

The 29C94, multi-channel HDLC controller, transmits data to, and receives data from, a Line Interface Unit (L.I.U.) PCM transceiver and framer such as MHS 29C3XX associated to the 29C96 in ISDN/DMI primary

The circuit is entirely compatible with ISDN specified by CCITT and supports connections of computers through the ISDN at the primary rate in HDLC protocol format. It also supports modes 0, 1, 2 and 3 of the DMI protocol for clear channels transmission of data at 64 kbps.

The 29C94 device provides additionnal functions which support ISDN hyperchannel and users defined protocols, and insure full compatibility with X25, LAPB and LAPD protocols.

These features allow the use of the 29C94 in a wide range of applications that go beyond the ISDN HDLC data links.

The 29C94 finds applications in several areas of telecommunication. This includes multimedia terminals and servers, network couplers (STARLAN, ETHERNET, ...), PABX signaling, PABX to Computers links, etc.

- On board 16-bit CRC generation and checking using CCITT polynomial, automatic flag detection and transmission, zero-bit insertion and deletion

- Independent and flexible transmit/receive PCM serial link

- Independent report on every transmit/receive channel activities through interrupt requests.

- Compatible with Motorola 680X0 and Intel 80X86.

- Programmable number of channel from 2 to 32 and loop back mode operations for test purposes.

- Operates from a single 5 V power supply.

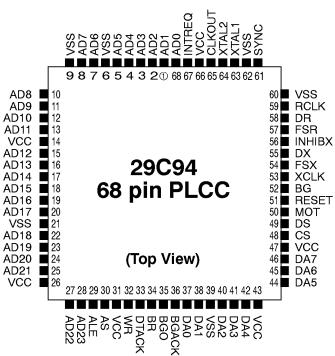

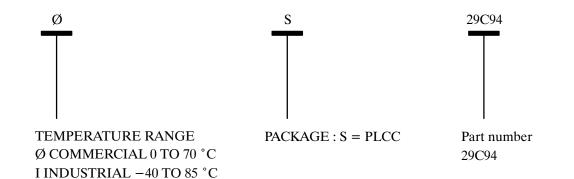

- Packaged in 68 pin PLCC

rate (2.048/1.544 Mbps). It stores and fetches the data to and from buffers allocated into an external memory, shared with the system host microprocessor as illustrated in the application example of Fig. 1.

# **29C94**

ΤΕΜΙΟ

MATRA MHS

#### Figure 1. Typical Application

29C94 pin assignments are shown on fig 2. Definitions of interface signals are given on Table 1.

#### Figure 2a. 29C94 Pin out.

# Figure 2b. Pin assignments

| PIN# I/O                                                                                                                                                                                                  | PIN# I/O                                                                                                                                                                                                                                     | PIN# I/O                                                                                                                                                                                                                             | PIN# I/O                                                                                                                                                                                                                                   | PIN# I/O                                                                                                                                                                                                        | PIN I/O                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $ \begin{array}{c cccc} -68 & AD_0 \\ -1 & AD_1 \\ -2 & AD_2 \\ -3 &AD_3 \\ -4 & AD_4 \\ -5 & AD_5 \\ -7 & AD_6 \\ -8 & AD_7 \\ -10 & AD_8 \\ -11 & AD_9 \\ -12 & .AD_{10} \\ -13 & AD_{11} \end{array} $ | $\begin{array}{c cccc} -15 & AD_{12} \\ -16 & AD_{13} \\ -17 & AD_{14} \\ -18 & AD_{15} \\ -19 & AD_{16} \\ -20 & AD_{17} \\ -22 & AA_{18} \\ -23 & AD_{19} \\ -24 & AD_{20} \\ -25 & AD_{21} \\ -27 & AD_{22} \\ -28 & AD_{23} \end{array}$ | $\begin{array}{ccccc} -37 & DA_0 \\ -38 & DA_1 \\ -40 & DA_2 \\ -41 & DA_3 \\ -42 & DA_4 \\ -44 & DA_5 \\ -45 & DA_{76} \\ -46 & DA_7 \\ -48 & \overline{CS} \\ -29 & ALE \\ -30 & \overline{AS} \\ -32 & \overline{WR} \end{array}$ | <ul> <li>- 33 DTACK</li> <li>- 34 BR</li> <li>- 52 BG</li> <li>- 35 BGO</li> <li>- 36 BGACK</li> <li>- 49 DS</li> <li>- 67 INTREQ</li> <li>- 51 RESET</li> <li>- 53 XCLK</li> <li>- 59 RCLK</li> <li>- 54 FSX</li> <li>- 57 FSR</li> </ul> | $\begin{array}{cccc} -55 & DX \\ -58 & DR \\ -56 & INHIBX \\ -61 & SYNC \\ -50 & MOT \\ -63 & XTAL1 \\ -64 & XTAL2 \\ -65 & CLKOUT \\ -14 & V_{CC} \\ -26 & V_{CC} \\ -31 & V_{CC} \\ -43 & V_{CC} \end{array}$ | $\begin{array}{ccc} -47 & V_{CC} \\ -66 & V_{CC} \\ -6 & V_{SS} \\ -9 & V_{SS} \\ -21 & V_{SS} \\ -39 & V_{SS} \\ -60 & V_v \\ -62 & V_{SS} \\ \end{array}$ |

#### Table 1 : 29C94 Interface Signal Definitions.

| Symbol                            | Туре | Name & description                                                                                                                                                                                             | Active | Active Mode   |  |  |

|-----------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|--|--|

|                                   |      | SYSTEM BUS INTERFACE – BUS MANAGER –                                                                                                                                                                           | INTEL  | MOTORO-<br>LA |  |  |

| AD <sub>0</sub> -AD <sub>23</sub> | I/O  | Address bus. Bidirectional address lines between 29C94 and the buffers or the host CPU and 29C94 internal registers.                                                                                           | N.A    | N.A           |  |  |

| DA0-DA7                           | I/O  | <b>Data lines.</b> Bidirectional data lines between 29C94 and the buffers or the host CPU and 29C94 internal registers                                                                                         | N.A    | N.A           |  |  |

| CS                                | Ι    | Chip select. Active low.                                                                                                                                                                                       | LOW    | LOW           |  |  |

| ALE                               | I/O  | Address Latch Enable. Tied to ground in MOTOROLA mode. A valid address is present on the address lines when ALE goes high in INTEL mode.                                                                       | HIGH   | N.A           |  |  |

| AS                                | I/O  | Address Strobe in MOTOROLA mode. Read strobe in INTEL mode                                                                                                                                                     | LOW    | LOW           |  |  |

| WR                                | I/O  | Write Strobe, to perform either a data write cycle into the system memory or a CPU write cycle into the 29C94 internal memory.                                                                                 | LOW    | LOW           |  |  |

| DTACK                             | I/O  | <b>Read/write acknowledge.</b> As an input, acknowledges DMA read or write cycles. As an output, acknowledges a CPU read or write cycle into the 29C94 internal RAM/registers.                                 | HIGH   | LOW           |  |  |

| BR                                | О    | <b>Bus request</b> . Open collector output to request system bus control take over.                                                                                                                            | LOW    | LOW           |  |  |

| BG                                | Ι    | Bus grant. To signal that 29C94 is granted system bus control.                                                                                                                                                 | HIGH   | LOW           |  |  |

| BGO                               | 0    | <b>Daisy chain bus grant output.</b> In a daisy chain, level asserting that HIG system bus control is granted to a daisy chained device.                                                                       |        | LOW           |  |  |

| BGACK                             | I/O  | <b>Bus grant acknowledge output.</b> Acknowledges that system bus is under 29C94 control.                                                                                                                      | N.A    | LOW           |  |  |

|                                   |      | Daisy chained bus request input. Forwards a bus request in a daisy chain.                                                                                                                                      | LOW    | N.A           |  |  |

| DS                                | Ι    | Data strobe. Pulse to read from, or write data into the 29C94                                                                                                                                                  | N.A    | LOW           |  |  |

| INTREQ                            | 0    | <b>Interrupt request.</b> Level to call host CPU attention after a buffer closing.                                                                                                                             | HIGH   | HIGH          |  |  |

| RESET                             | I    | <b>RESET.</b> Pulse to reset global mode control registers. Minimum pulse width is two PCM frame periods. Reset causes the 29C94 to default in HDLC mode, de-activates all channels, puts all 0s in fill/mask. | HIGH   | LOW           |  |  |

#### Table 1 : 29C94 Interface Signal Definitions.

| Symbol | Туре | Name & Description                                                                                                                                                                                            | Active Mode                          |  |  |  |  |

|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|--|--|

|        |      | PCM HANDLER                                                                                                                                                                                                   |                                      |  |  |  |  |

| XCLK   | I    | <b>Transmit bit clock</b> . Square wave input from the LIU clock generator providing the master timing source for the transmit channel. Frequency is 2.048/4.096 Mbps in CEPT, or 1.544/3.088 Mbps in T1/DS1. |                                      |  |  |  |  |

| RCLK   | Ι    | <b>Receive bit clock</b> . Same as the XCLK input, except that applies to the receive channel                                                                                                                 |                                      |  |  |  |  |

| FSX    | I/O  | <b>Transit frame sync.</b> Pulse for frame synchronisation. Frequency is 8 kHZ. Input in slave operating mode Output in master operating mode.                                                                | HIGH                                 |  |  |  |  |

| FSR    | I/O  | <b>Receive frame sync.</b> Same as the FSX input, except that applies to the receive channel                                                                                                                  | HIGH                                 |  |  |  |  |

| DX     | 0    | <b>Transmit data</b> . Output of 29C94 to the LIU representing the transmit serial data bit stream.                                                                                                           |                                      |  |  |  |  |

| DR     | Ι    | <b>Receive data.</b> Input from the LIU representing the received serial data bit stream.                                                                                                                     |                                      |  |  |  |  |

| INHIBX | 0    | <b>Transmit time slot inhibit.</b> Level to the LIU asserting that transmit function of current time slot is inhibited.                                                                                       | HIGH                                 |  |  |  |  |

| SYNC   | Ι    | <b>Sync.</b> Input from the LIU asserting that receive PCM from alignement is correct.                                                                                                                        | HIGH                                 |  |  |  |  |

|        |      | OPTIONS                                                                                                                                                                                                       |                                      |  |  |  |  |

| МОТ    | Ι    | <b>MOTOROLA/INTEL</b> . Input to select system bus interface type. Low high level input selects MOTOROLA interface.                                                                                           | level input selects INTEL interface, |  |  |  |  |

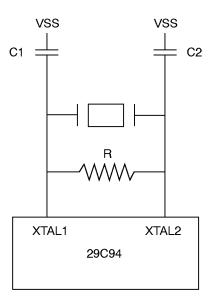

| XTAL1  | I    | Input of crystal oscillator or external chip clock.                                                                                                                                                           |                                      |  |  |  |  |

| XTAL2  | 0    | Crystal oscillator output.                                                                                                                                                                                    | Crystal oscillator output.           |  |  |  |  |

| CLKOUT | 0    | Chip clock buffered output.                                                                                                                                                                                   |                                      |  |  |  |  |

| VCC    | I    | <b>SUPPLY.</b> + 5 Volt power supply.                                                                                                                                                                         |                                      |  |  |  |  |

| VSS    | Ι    | GROUND. Power supply ground.                                                                                                                                                                                  |                                      |  |  |  |  |

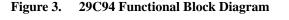

# **1.0 Functional Description**

The 29C94 multiplexes/demultiplexes up to 32 full duplex channels over the time slots of the PCM frames. Two or more, adjacent or non adjacent, time slots may be dynamically concatenated to form an hyperchannel.

Data to be transmitted are fetched through DMA cycles in 8-bit parallel form, time slot after time slot, from the buffers; they are processed by performing protocol data formatting and rate adaptation, then transmitted in serially to the PCM link.

Conversely, the incoming stream of serial data is processed, channel by channel, by performing rate adaptation and data frame protocol deformatting ; received data are stored, through DMA cycles, in 8-bit parallel form into the channel allocated buffers. Each channel is allocated eight chained buffers to transmit data and the same amount on receiving side. Buffers have a maximum capacity of 64 kbytes.

Overall 29C94 can address up to 512 buffers of 64 kbytes each.

The internal functions of the 29C94, controlled by the registers, are partitionned into 5 major operating logic blocks as shown in Fig. 3 below.

1 - PCM HANDLER, 2 - HDLC PROCESSOR,

3 - DMA CONTROLLER, 4 - BUS MANAGER.

5 - CONTEXT MONITOR.

# **29C94**

Each channel is processed depending on the operating modes specified by the device internal control registers that the host CPU initializes and sets up. Device initialisation is explained later on when describing the details of the registers. Two types of operating modes are programmable.

**A) - Global operating mode :** It applies to every channels and selects :

- CEPT 32 channels vs T1/DS 24 Channels

- Test mode vs (CEPT-T1/DS1) mode

- PCM Slave mode

PCM Simple

clock mode

Vs PCM Master mode

vs PCM Double clock

mode (GCI)

- All channels valid vs All channels unvalid

- PCM frame sync offset control.

- Loop back operation for test purpose

Specifying the global operating mode requires six 8-bit words. Eight more bytes of global registers are reserved for interrupt request purposes, which the 29C94 initiates itself.

#### **B) - Channel operating mode :**

Within the global mode, it is programmable on any channel independently of every others. Furthermore, on

| Table 2 : Register Mapping into Internal 1 | RAM. |

|--------------------------------------------|------|

|--------------------------------------------|------|

any channel, the receive mode is independent of the transmit mode.

For both, transmit and receive sides, the programmable channel mode parameters are :

- HDLC mode

- vs Clear channel mode

- Time slot valid vs Time slot unvalid

- Flag sharing enable/disable (Transmit only)

- Rate adaptation/fill-mask,

- Channel number,

- Buffers descriptors/: Buffer size/word count

DMA descriptors (16 bits),

Start address (24 bits),

Processing status.

Receive and transmit parameters that are specific to a time slot and that control the data processing during that time slot will be referred thereafter as the "*time slot context*" or "*context*". They are maintained inside the 29C94, stored in an internal RAM and accessed through the "CONTEXT MONITOR" functional logic block. Context specification is allocated 128 bytes per time slot : 64 bytes for transmit context and 64 bytes for the receive context.

Mapping of the internal RAM is shown table 2 below. Register definitions and functions are given starting on chapter 3.0.

| Mod    | es     | Addresses                                            | RAM/Register Mapping                         |

|--------|--------|------------------------------------------------------|----------------------------------------------|

|        |        | $0_{\rm H}$ to $3F_{\rm H}$                          | Receive context ; Time slot 0                |

|        |        | $40_{\mathrm{H}}$ to $7\mathrm{F}_{\mathrm{H}}$      | Receive context ; Time slot 1                |

|        | R      |                                                      |                                              |

|        | E<br>C |                                                      | Receive context ; Time slot N-1              |

| С      | Е      |                                                      | Receive context ; Time slot N                |

| Н      | I<br>V |                                                      | Receive context ; Time slot N+1              |

| A<br>N | E      |                                                      |                                              |

| N      |        | $7A0_{\mathrm{H}}$ to $7CF_{\mathrm{H}}$             | Receive context ; Time slot 30               |

| E<br>L |        | $7 \text{C0}_{\text{H}}$ to $7 \text{FF}_{\text{H}}$ | Receive context ; Time slot 31               |

| L      |        | $800_{\mathrm{H}}$ to $83F_{\mathrm{H}}$             | Transmit context ; Time slot 0               |

| М      |        | $840_{\mathrm{H}}$ to $87F_{\mathrm{H}}$             | Transmit context ; Time slot 1               |

| 0      | T<br>R |                                                      |                                              |

| D<br>E | А      |                                                      | Transmit context ; Time slot N-1             |

|        | N<br>S |                                                      | Transmit context ; Time slot N               |

|        | M      |                                                      | Transmit context ; Time slot N+1             |

|        | I<br>T |                                                      |                                              |

|        |        | $\rm F80_{H}$ to $\rm FBF_{H}$                       | Transmit context ; Time slot 30              |

|        |        | $FCO_H$ to $FFF_H$                                   | Transmit context ; Time slot 31              |

| GLOBAL | MODE   | $1000_{\mathrm{H}}$ to $100\mathrm{D}_{\mathrm{H}}$  | Global mode parameters and interrupt request |

Global operating mode parameters are permanently applied to the functional logic blocks as they do not change from one time slot to the other, except for a deliberate CPU intervention. On the contrary, the context parameters, pertaining to a specific time slot, are switched on every time slot. Context switching is performed by the CONTEXT MONITOR, as explained further on.

To summarize : On each successive time slot of the PCM frame and within the global operating mode, specific time slot context is retrieved from the internal RAM at the beginning of the time slot. Processing actions then take place over the time slot length, according parameters of the context, which, by the end of the slot, is updated and saved until its next occurence in the PCM frame, 125  $\mu$ s later.

Let us remark that during a time slot (3.9  $\mu$ s in CEPT), assuming it is valid and there are data being received and transmitted on this channel, several discrete actions are taking place ; ie. Context restoring- updating-saving, data fetching (transmit) and storing (receive), current CRC computation, serial data processing (transmit/receive), etc... To do so, the 29C94 operates at an internal frequency of up to 33 MHz (30 ns period) driven either by an external clock or an internal crystal oscillator as shown on AC Electrical Characteristics. Furthermore, the 29C94 uses throughout its synchronous design a pipeline architecture. Pipeline operations are illustrated fig. 4 below.

The CONTEXT MONITOR also provides, through the BUS MANAGER, a path to the host CPU for accessing the internal RAM and thus, all registers.

#### Figure 4. Context Monitor pipe-line.

|                 | PCM Frame       | -               |  |

|-----------------|-----------------|-----------------|--|

| Time slot N–1   | Time slot N     | Time slot N+1   |  |

| Read context    | Read context    | Read context    |  |

| time slot N     | time slot N+1   | time slot N+2   |  |

| Execute context | Execute context | Execute context |  |

| time slot N–1   | time slot N     | time slot N+1   |  |

| Save context    | Save context    | Save context    |  |

| time slot N–2   | time slot N–1   | time slot N     |  |

# 2.0 Functional Logic Blocks

Functional logic blocks performances are controlled and driven from the global and context registers, which mapping in the 29C94 internal RAM is shown in Table 2. A quicker understanding of the logic blocks operations will be helped by looking at details of the control register contents in the "REGISTER DEFINITION", starting on chapter 3.0.

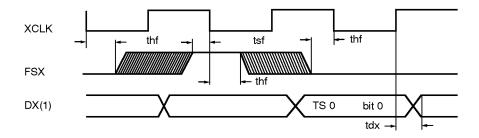

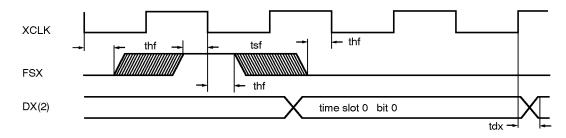

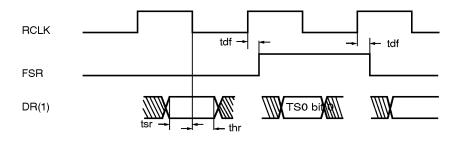

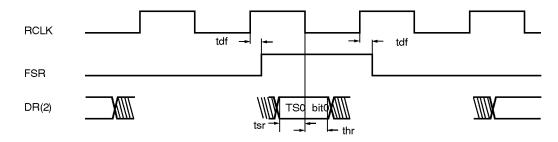

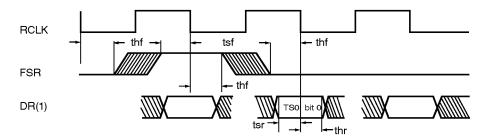

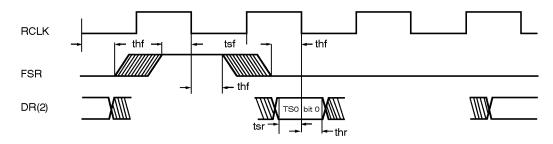

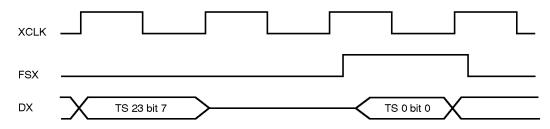

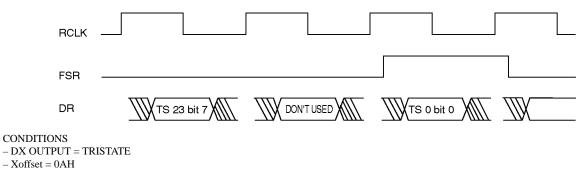

# 2.1. PCM Handler

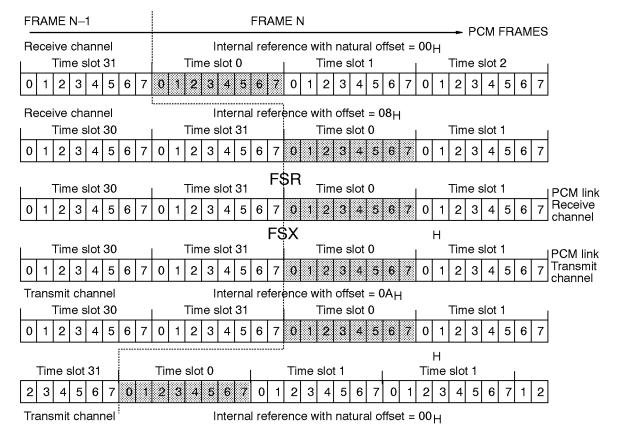

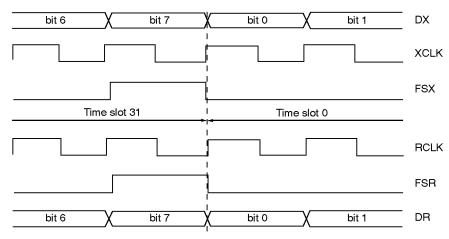

The PCM HANDLER is mostly controlled by the global registers : *MODE*, *ROFFSET*, *XOFFSET*, *GLOBINH*, *TEST* and *TESTEXT*. It transmits, on DX output, and receives, on DR input, serial data from a L.I.U. device as shown in fig. 1. It performs receive/transmit data synchronization using XCLK and RCLK clock inputs and generates an internal reference, bit 0/time slot 0, with an adjustable offset against the external PCM frame syncs,

FSR/FSX. It also supplies the bit clock to the HDLC PROCESSOR logic block.

The whole 29C94 is programmable in either master or slave mode with respect to FSX and FSR frame sync (see *MODE* global register on chapter 3.2).

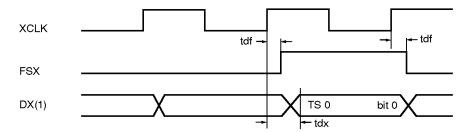

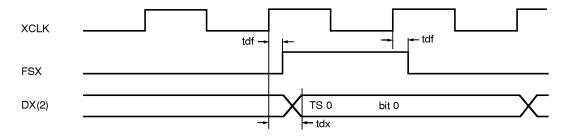

<u>SLAVE mode</u>: Frame sync, FSX/FSR, and bit clock, XCLK/RCLK, are input signals. Width of FSX/FSR pulses must be at least one XCLK/RCLK period.

<u>MASTER mode</u>: The 29C94 generates the frame sync FSX/FSR. They are derived from XCLK/RCLK bit clock inputs. FSX/FSR pulse widths are equal to one XCLK/RCLK period.

XCLK and RCLK bit clocks may be asynchronous, however the loop back mode is not then possible.

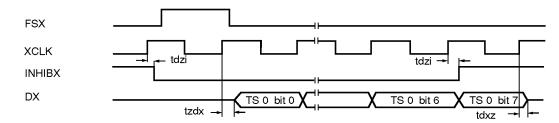

**DX** output driving mode is programmable as "tri-state", or "always high" or "wired OR" (See DXC0, DXC1 in

*MODE* chapter 3.2). DX is forced to "1" or high impedance when the time slot is not valid.

**SYNC** input is used in conjonction with a FRAMER device, such as the MHS 29C96. SYNC asserts the status of the received frame, according the truth table below.

| SYNC  | "1"          | "0"              |  |  |

|-------|--------------|------------------|--|--|

| Frame | synchronized | not synchronized |  |  |

When SYNC goes low, incoming data is ignored on every time slot and a bit (Lsyn) is automatically set into *RCTST* status registers of all channels (Receive DMA descriptors chapter 3.11). Received data will again be only considered and only stored after SYNC recovery.

Whenever a framer device is not used, the SYNC input pin must be tied to Vcc.

**INHIBX** asserts that the current time slot is inhibited. This output goes high, one bit clock period before the related time slot. INHIBX may be used with a framer device to force a preset idle code during the inhibited time slot. That feature is specially usefull with AMI coding in T1/DS1 application.

# FRAME SYNC OFFSET. (*ROFFSET* and *XOFFSET* registers, chapter 3.3)

Because of inherent design delays, the internal PCM frame reference-bit 0/time slot 0 – must be shifted so that, seen from the outside, it appears in sync with the FSX/FSR PCM link. Offsets are separately programmable on both transmit and receive side, either in CEPT or T1/DS1 mode.

Programming resolution is one bit clock period (1/2 bit clock resolution in double clock mode). Loop back mode is only possible when transmitter and receiver are synchronous and that transmit and receive channels are aligned. That is to say when both the external transmit and receive time slot references appear at the same time (same bit clock, same FRAME SYNC as shown fig 6). Fig. 5 below, shows the natural internal reference offsets against the external FSX/FSR ISDN line.

#### Figure 5. Internal References and Offsets.

Natural offset values are 8 bit clock on the receive side and 10 bit clock on the transmit side. Thus, assuming that a given application brings in additional delay worth N bit clock, the minimum offset programming on the *ROFFSET* register becomes  $08_{\rm H}$ +N ( $10_{\rm H}$ +2N in double clock mode) and will be OA<sub>H</sub>+N ( $14_{\rm H}$ +2N in double clock mode) on the **XOFFSET** register.

Delays on transmit and receive channels were designed different because of 29C94 synchronous design and its full duplex capability. On every time slot the transmit channel is processed first, two bit clock periods (1  $\mu$ s in CEPT mode) before the receive channel. A side effect of this feature is to possibly allow, on a given time slot, a

successfull receive DMA cycle completion, even if a time out has occured on the transmit DMA cycle.

As shown on the diagram figure 6, in slave mode, single clock, assuming that the transmit offset register is properly set, bit 0/time slot 0 of the transmit frame is output on first XCLK rising edge after FSX has been sampled to 1 by XCLK falling edge.

Similarly, if the receive offset register is correctly set, bit 0/time slot 0 of the received frame is sampled on the first RCLK falling edge after FSR was sampled to 1 by RCLK falling edge.

#### Figure 6. Offset Programming.

## 2.2. HDLC Processor

The HDLC PROCESSOR logic block is mostly driven and controlled by the context HDLC descriptor. It receives data bytes from the DMA CONTROLLER, processes and transfers them in series, LSB first, to the PCM HANDLER. Conversely, it receives data in series from the PCM HANDLER and, processes and sends them in byte form to the DMA CONTROLLER. The HDLC PROCESSOR also performs data rate adaptation with fill registers (transmit) or mask registers (receive).

The HDLC PROCESSOR is shared and successively used by all channels of the PCM frame. It is programmable in either HDLC or clear channel mode (see *RMOD* and *XMOD* registers, chapter 3.7).

#### HDLC Mode

In that mode basic HDLC frame formating is performed, as shown in figure 7.

Figure 7. HDLC Framing Format

| 7E <sub>H</sub> | $N \times 8$ bits | $2 \times 8$ bits | 7E <sub>H</sub> |  |

|-----------------|-------------------|-------------------|-----------------|--|

| Flag            | Data              | CRC               | Flag            |  |

Frame check sequence (CRC) is computed from CCITT polynomial :  $X^{16} + X^{12} + X^5 + 1$ . Frame length is 64 kbytes maximum, plus flags and CRC. A data frame is always contained into one single buffer.

On any channel, flag sharing capability between successive transmitted data frames is programmed by setting up to "1" the **FLG**-bit into the *XMOD* register. In that mode the same flag may close a data frame and open the next frame.

#### Transmit :

Upon transmission the HDLC PROCESSOR performs protocol formatting and composes the HDLC frames with the data fetched in the buffers by the DMA

# **29C94**

CONTROLLER. It generates flags, abort and idle codes, inserts one "ZERO" after five consecutive "ONES" and computes the HDLC frame check sequence (CRC).

Flags are stuffed when there is no valid data to transmit while the time slot is valid.

Data frame closing occurs when either the related transmit data buffer is empty, (word count = 0), or after an unsuccessfull DMA attempt (time-out).

In the first case, a flag closes the frame and flags proceed to be sent while the time slot is valid with no data to transmit. In case of time out, the frame is closed with an **Abort** ( $\mathbf{FF}_{H}$ ) character. In both cases, a report is assembled and stored in the *XCTST* register of the related DMA descriptor.

#### Receive :

On the receive side, the HDLC PROCESSOR extracts serial data from the incoming stream on PCM HANDLER and performs protocol deformatting. It detects flags, abort and idle codes, suppresses inserted zeroes, checks the HDLC frame check sequence (CRC). The resulting serial data is transferred to the DMA CONTROLLER to be stored in the buffers. All incoming bits following the detection of a flag ( $7E_H$ ) are assembled in byte character.

Frame reception may be interrupted for various reasons outlined below. In all cases, the cause is reported, as

explained hereafter, and stored into the related *RCTST* register of the DMA descriptor.

- Closing flag  $(7E_{\rm H})$  detection (**FTR** bit set to "1"),

- abort character (FF<sub>H</sub>) detection (ABRT bit set to "1")

- lost of Sync, (SYNC, pin# 61, = 0), (LSYN bit set to "1")

- buffer full with yet a byte to store, (**UDF** bit set to "1")

- DMA attempt is unsuccessfull, (TOUT bit set to "1")

- attempt to use an unvalid buffer, (**DONE** bit set to "1")

A minimum of 4 bytes (2 data bytes + CRC) is required between 2 flags.

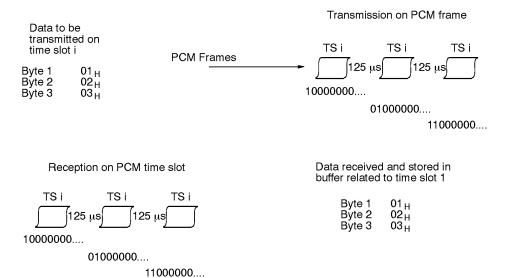

#### CLEAR Channel Mode

Flag generation/detection, bit insertion and CRC computing are disabled in clear channel mode. Buffers are automatically chained, one after another. Frame length is not limited to one buffer as in HDLC mode.

"Ones" are transmitted when data are not available or upon a DMA time out. As in HDLC mode, a status is assembled in that later event (*RCTST* and *XCTST* status registers, chapter 3.11).

If the DMA CONTROLLER chains to a DMA descriptor that is not empty, then writing is not executed in the pointed buffer neither in the status register. Data characters alignment is kept on the PCM time slot. Following is an example of transmit/receive clear channel, 64 kbps, on time slot i.

#### Rev. E (29/09/94)

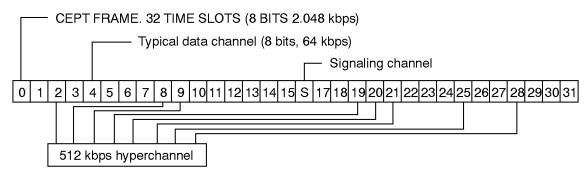

#### **Hyperchannel**

In both, HDLC or Clear channel modes, data may be received or transmitted over an **hyperchannel** that is made of the concatenation of adjacent, or non-adjacent,

#### Figure 8. 512 kbps hyperchannel

represented.

The example illustrates a 512 kbps hyperchannel made of eight adjacent *and* non-adjacent time slots within the CEPT frame. This results in a PCM frame with twenty five channels. Twenty four of them are single 64 kbps channels and the last is the 512 kbps channel. Up to 31 time slots can be concatenated to form a 1.984 Mbps hyperchannel.

A time slot is recognized as part of an hyper channel when its "channel number" is different from its time slot number. The PCM counters (Transmit/receive) keep track of the time slot number while the channel number is user defined and stored into the related *RMOD/XMOD* register in the HDLC descriptor part of the time slot context.

time slots as shown on fig.8, where the CEPT frame is

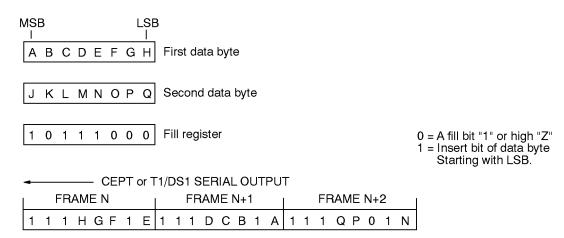

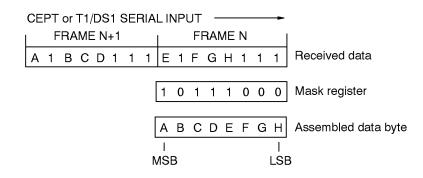

#### Rate Adaptation (See RSPEED and XSPEED registers)

Receive and/or transmit data rate is adaptable on every channel. Basic 64 Kbps rate may be adapted to subrates that are 8 kbps multiples (8, 16, 24, ...). Fill/mask registers

are applied to shift registers that data is passing through as illustrated in fig. 9a and 9b.

#### Figure 9a. Transmit Rate Adaptation : Single transmit channel 24 kbps.

A bit set to "0" in the *XSPEED* register forces DX output to "1" or "High Z", according to DX driving mode. A "1" in the fill register let the data bit being output.

A bit set to "0" into the mask register, prevents the corresponding received data bit to be latched into the 29C94. Only when a full byte has been assembled, it will be transfered towards the buffer.

Figure 9b. Receive Data : Single receive channel 24 kbps.

## 2.3. DMA Controller

The DMA CONTROLLER is mostly driven and controlled by the DMA descriptor, part of the time slot context control registers. It manages in and out data transfers between the HDLC PROCESSOR and buffers in the system memory. Data fetching and storage are achieved over the host CPU bus through a direct memory access cycle (DMA).

The DMA cycle takes place, when requested, inside the time slot period.

Bus contention is monitored by the 29C94 BUS MANAGER logic block which checks that the bus is available before allowing buffers access to the DMA CONTROLLER (see chapter 2.4 DMA CYCLE). DMA request is done each time a new data byte has to be, either transmitted or stored. Finally the DMA CONTROLLER checks that, before the end of the time slot, the DTACK signal (pin#33) is asserted, pointing out that the DMA cycle is complete. When it is not so, a time out is generated and the cycle aborted.

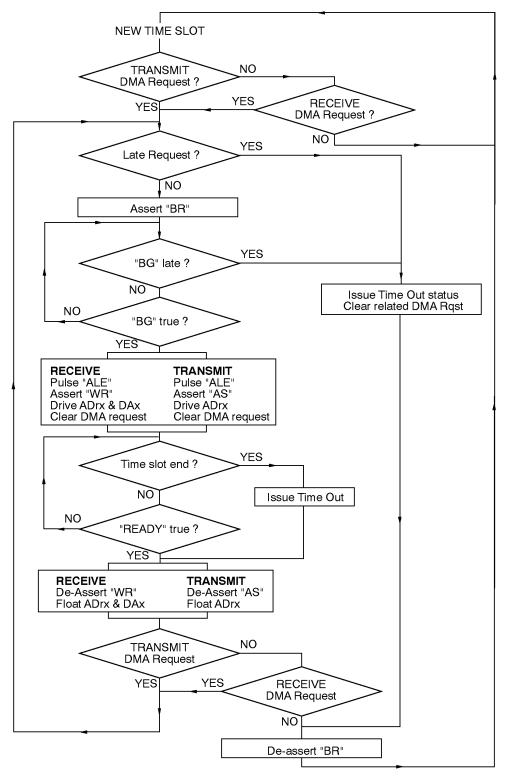

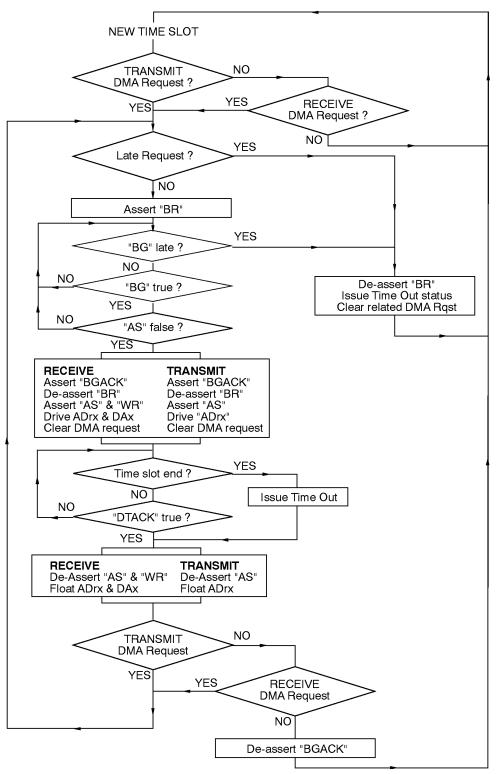

DMA cycle flow charts are shown in figure 10 and 11.

Each channel is allocated eight transmit buffers and eight receive ones. Channel Buffer addresses are maintained in the DMA descriptor that is part of the context (time slot context mapping in tables 8 and 9).

Initialized by the host CPU, the eight DMA descriptors contain :

In high impedance driving mode, up to eight 29C94 DX

outputs may be connected in parallel. Mutually exclusive

fill registers could then be used to make subrate time

division multiplexing over the 64 kbps channel.

| _ | Word | count/D | ata frame length. | 16 bits |

|---|------|---------|-------------------|---------|

|   | D 66 | 1 1     | •                 | 1 < 1 * |

- Buffer address pointer 16 bits

- DMA status 8 bits

- Buffer page address. 8 bits

All the transmit/receive descriptors may be initialized in advance, so as to be ready when the transmit/receive activity is starting.

#### Transmit :

Each time a DMA transfer is successfully completed the word count is decremented and current address (pointer) incremented until that either the buffer is exhausted (word count=0) or a time out occurred. In any event, a status report is assembled then stored in *XCTST* register and the buffer index in *XSTAT1* register is incremented, modulo 8, to point to a new buffer. Each time there is a switch over in buffer index, an interrupt request is asserted through the set up to "1" of the ITX(x) bit in the *XINTRQ* global registers, with (x) being the channel number (see chapter 3.5).

Upon interrupt request the CPU reads into the 29C94 *INTRQ* registers, memorizes all interrupt requests, resets the registers and re-initializes the buffers that triggered the interrupt.

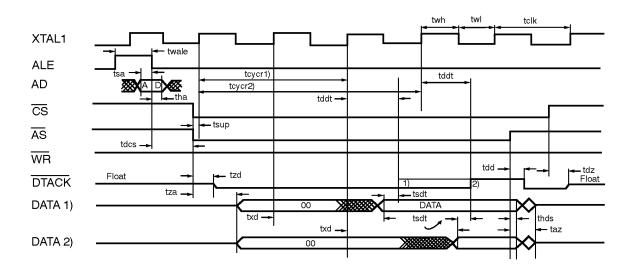

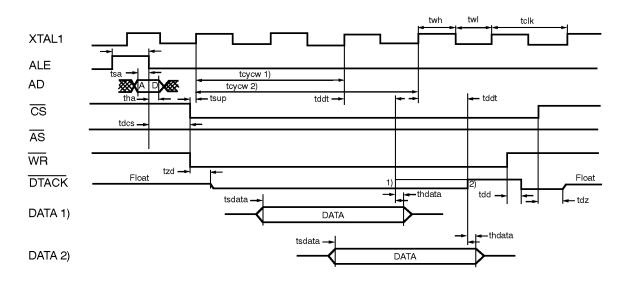

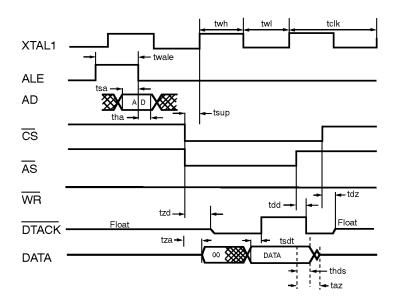

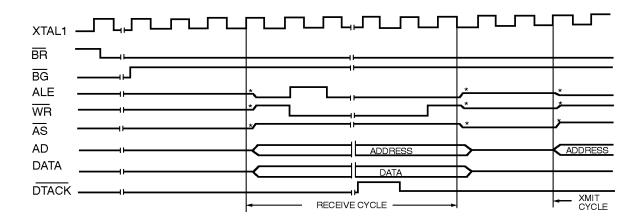

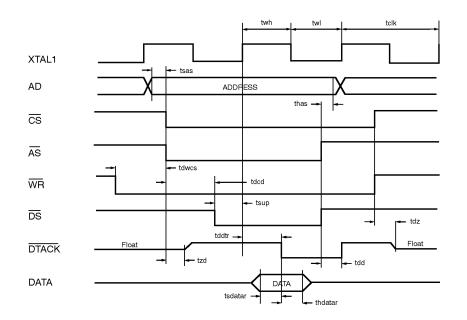

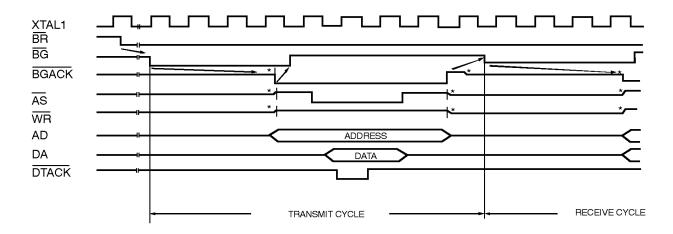

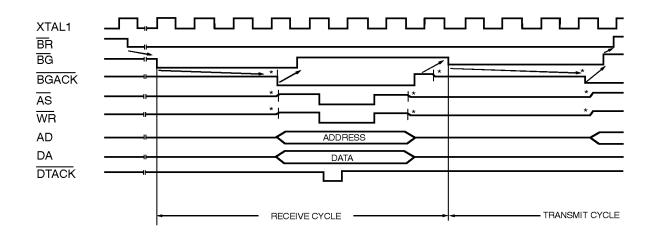

#### Figure 10. DMA cycle with INTEL host CPU.

Note : Transmit and/or receive DMA requests rise, if they are present, when time slot begins.

Note : Transmit and/or receive DMA requests rise, if they are present, when time slot begins.

As soon as the system bus is granted, the transmit DMA cycle starts with AD (23:0) address output on system bus and AS/ALE/WR signals being asserted. The cycle ends

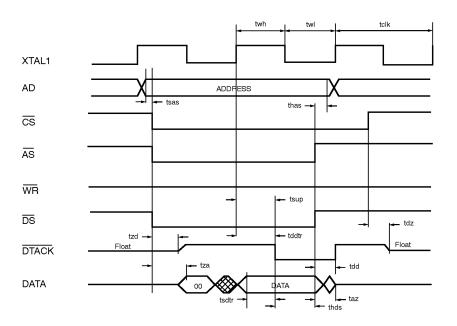

#### Receive :

The whole process for DMA transfer of received data is very much like the transmit one, except that buffer status and buffer indexes are respectively reported in receive channel RCTST and RSTAT1 registers. In the same way, buffer switching is reported in ITR(x) thus triggering an interrupt request, which is CPU processed as explained above.

The receive DMA cycle starts with address, AD (23:0), and data, DA (7:0), output on system bus, and AS/ALE/WR signals being asserted. The cycle normally ends with DTACK (write acknowledge) asserted before the end of time slot.

In case of overflow (WC=0 and frame not finished) or in

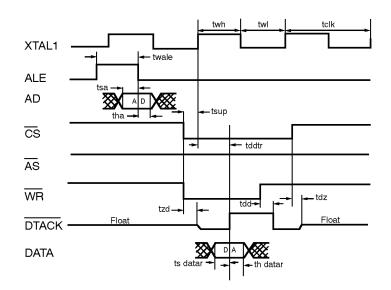

## 2.4. Bus Manager

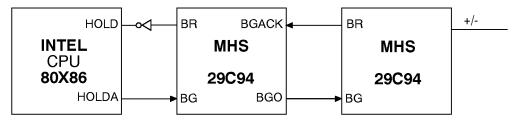

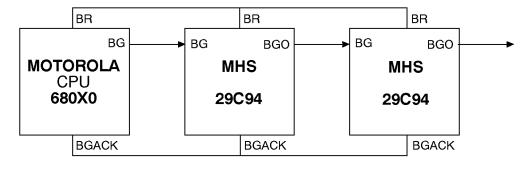

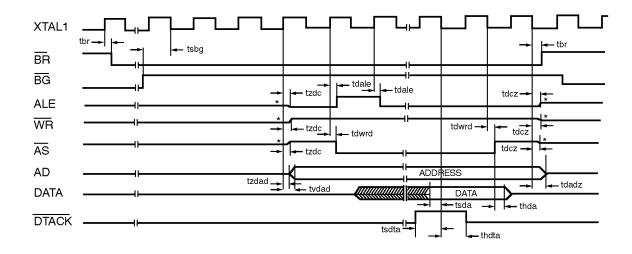

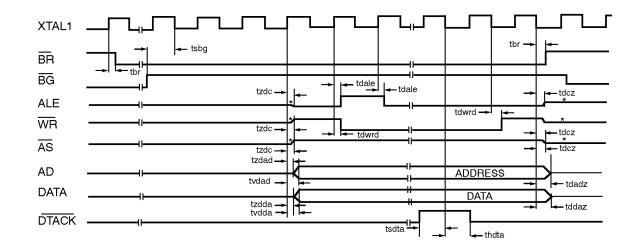

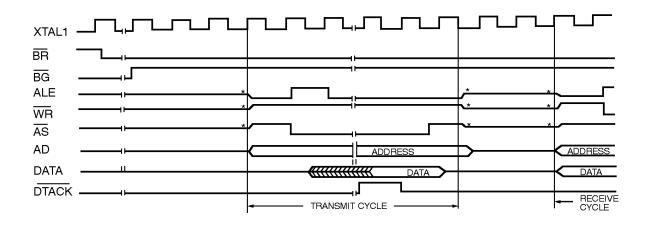

The BUS MANAGER interfaces the 29C94 internal logic blocks with the system bus (see fig. 3). **MOT** input (pin#50) selects either INTEL or MOTOROLA interface types. The BUS MANAGER responds to commands originating from the DMA CONTROLLER (DMA request), or from the interrupt registers, or from the host CPU. The BUS MANAGER performs system bus take over for DMA cycles. Also, upon buffers switching, it generates interrupt requests that call for CPU actions. System bus take-over is accomplished after a **bus request/bus grant** hand-shake with the host CPU (BR pin#34/BG pin#52), authorizing the BUS MANAGER to drive the system bus. Timing diagrams are shown on chapter 6.1 to 6.9 for an INTEL CPU and chapter 7.1 to 7.9 for a MOTOROLA CPU.

The 29C94 data bus interface,  $D_0$  through  $D_7$ , needs to be only 8-bit wide due to the low demand in data exchange. The interface address bus is 24-bit wide,  $AD_0$  through  $AD_{23}$ , allowing 512 buffers of 64 kbits each. Only bit  $AD_0$  through  $AD_{12}$  are used when the CPU accesses the 29C94 internal RAM/registers. The 29C94 automatically generates the acknowledgement, DTACK (pin#33), (READY in INTEL mode), when its RAM/registers are being accessed. It also waits for DTACK (READY in INTEL lode) acknowledgement to complete a DMA cycle.

#### CPU Access

The CPU accesses the global registers (Read/write) within three XTAL1 clock cycles maximum. Context

with a DTACK (see DMA flow chart on figures 10 and 11).

case of loss of sync (SYNC = 0) the current buffer is automatically closed and the 29C94 looks up for next opening flag.

If a time out occurs, the current buffer is closed, the buffer index incremented but the incoming data stream is ignored until detection of a new flag.

If the buffer index points to a DMA descriptor that has an exhausted buffer (**DONE** not reset), then writing into the buffer will not be allowed nor in the *RCTST* register.

If all DMA buffers are exhausted, current buffer incrementation is stopped until buffers are re-initialized by CPU. Then flags are forced on transmit side and the receiver ignores incoming data stream.

registers access needs six XTAL1 periods maximum. Timing diagrams are shown on chapters 6.3 and 6.4 for INTEL CPU and chapters 7.3 and 7.4 for MOTOROLA.

The internal RAM looks like a dual port memory, which access is managed by the CONTEXT MONITOR. One port, 8-bit wide, is the path for the CPU through the BUS MANAGER, the other port, 16-bit wide, is the path to the functional logic blocks (see fig. 3 - 29C94 block diagram).

Because of delays to clock in and out of the RAM the context data (128 bytes to save/retrieve), compounded by the RAM own access time, the XTAL1 clock frequency cannot go lower than a limit fixed by the conditions listed below – worst case CEPT mode, shortest 3.9  $\mu$ s time slot :

$\begin{array}{ll} 1. - 3.9 > (2/F) \times (44 + N) \\ 2. - 3.9 > (1/F) \times 5N \\ 3. - 3.9 > ((2/F) \times N)^*3 \\ 4. - 3.9 > (1/FCPU) \times I \times N \\ \\ Where N = & number of CPU access \\ & to the internal RAM, \\ F = & XTAL1 \ frequency in \end{array}$

F = XTAL1 frequency in MHz, I = maximum number of CPU clock

periods for one R/W access.

1. Is the condition for a full transmit/receive context exchange.

Reflects that the CPU read or write cycle into context registers, takes a minimum of five XTAL1 periods.

Is related to the design of the CONTEXT MONITOR that allows one CPU access every two RAM accesses.

Relates to the CPU own read/write limitations.

With the recommended XTAL1 clock frequency of F = 33 MHz, in CEPT mode, all conditions are true. Then 22 R/W accesses may be completed on the CPU port, thus giving it a bandwith of 5.64 Mbytes/s. That throughput allows the host to update DMA descriptors of a given channel while the DMA CONTROLLER is using part of the descriptor. The conditions also apply to T1/DS1 mode, except that the time slot lasts 5.2 µs instead of 3.9 µs.

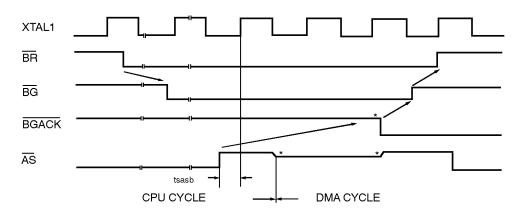

#### DMA Cycle

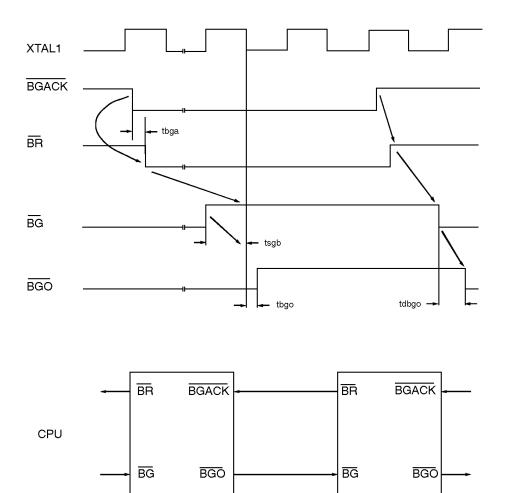

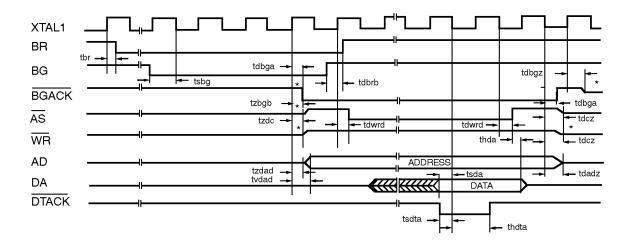

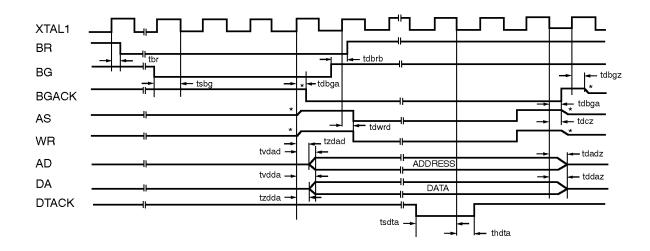

Upon DMA request, the BUS MANAGER issues a bus request, BR, and wait for BG, the bus grant signal. Additionally, in MOTOROLA mode, a bus grant acknowledge (BGACK) is issued by the 29C94.

In MOTOROLA mode BR/BG handshake begins the DMA cycle, and the BGACK output is kept true until the end of the cycle. In INTEL mode BR is kept true until the end of the cycle.

Over the whole cycle, the 29C94 controls the system bus. It drives the 24 bit address, the AS (READ), WR, ALE (in INTEL mode), strobes, and, for data write, the DATA lines. It checks for DTACK (READY).

AS (READ) WR and ALE (in INTEL mode) are de-asserted (AS=WR=1, ALE=0) at the beginning of the cycle, and de-asserted again by the end of the cycle.

Such feature simplifies the application design when selecting PULL-UP and PULL-DOWN resistors.

#### DMA timing considerations

At the beginning of a time slot, the BUS MANAGER scans for transmit and/or receive DMA request. If at least one is true, the DMA cycle starts. Therefore, on a given

time slot, there may be :

- No DMA or,

- either one read or one write cycle (either transmit or receive), or

- two cycles, one read and one write.

The BUS MANAGER checks that DMA cycle completion has, or may occur. According to the conditions, it will take the following actions :

- De-assert BR, bus request, if BG, bus grant, is not yet true by the end of time slot,

- abort the read or write cycle, de-assert BR and release the system bus, if memory acknowledge is not true before time slot end,

- abort the DMA cycle, if BG is asserted close to the end of the time slot, which would make a read or write cycle impossible.

In all cases, a time out status is reported causing a data frame abort on transmit side or a frame error on the receive side. The longest period allowed to achieve a DMA cycle is DELMAX and is worth :

DELMAX=(Time slot period) – (0.5 bit-clock periods) – (4 XTAL1 periods)

If XTAL1 frequency is the recommended 33 MHz, then :

# DELMAX = 3.5 $\mu s$ in CEPT mode or 4.6 $\mu s$ in T1/DS1 mode

Deadlock cannot occur because the circuit automatically recovers from unsuccessfull DMA attempt, such as trying to write or read into unexisting buffer addresses. When one read and one write cycle are requested on a given time slot, the BUS MANAGER does not de-assert BR after completion of the first cycle to save bus grant latency time.

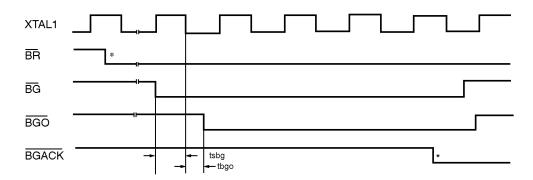

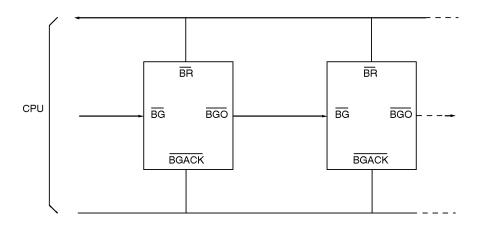

#### Daisy Chain Mechanism

The 29C94 includes an internal daisy chain logic circuit to help designing systems built with several devices that have, each, a system bus control take over capability. The internal daisy chain control saves PC board space compared to using a bus arbiter circuit. Signals involved in the daisy chain are shown in Table 3 below. Timing diagrams appear on chapter 6.10 (INTEL) and 7.11 (MOTOROLA)

| Table 3 | : | Daisy | Chain | Truth | Table |

|---------|---|-------|-------|-------|-------|

|---------|---|-------|-------|-------|-------|

| Signals                        |         | MOTOROLA | INTEL |

|--------------------------------|---------|----------|-------|

| BUS REQUEST OUTPUT             | – BR    | LOW      | LOW   |

| BUS GRANT INPUT                | – BG    | LOW      | HIGH  |

| DAISY CHAIN BUS REQUEST INPUT. | – BGACK | N.A      | LOW   |

| BUS GRANT ACKNOWLEDGE OUTPUT.  | – BGACK | LOW      | N.A   |

| DAISY CHAIN BUS GRANT OUTPUT.  | – BGO   | LOW      | HIGH  |

In INTEL mode (Fig. 12a), the 29C94 senses, the daisy chain bus request BGACK. When true the 29C94, forwards its own bus request, BR, on the chain. The last 29C94 waits for bus grant, BG, and, when true, will

forward it back to its BGO output if no DMA is requested from the DMA CONTROLLER. Internal DMA requests have priority over the daisy chain request and are executed first.

#### Figure 12a. INTEL Daisy Chain

In MOTOROLA mode (Fig. 12b), all the devices in the chain issue their bus request, BR, on the same line. Only the bus grant, BG, is chained. When a 29C94 receives a bus grant on its BG input, it forwards it to its bus grant

output, BGO, along the chain if no internal DMA is requested from the DMA CONTROLLER. Again DMA requests have priority over the daisy chain request.

## 2.5. Interrupt Controller

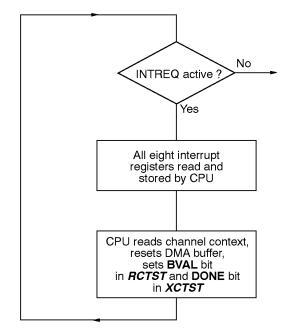

The interrupt controller generates an interrupt request each time a DMA buffer is closed (end of frame with normal or error status). The CPU identifies the interrupting channel by reading the eight 8-bit interrupt registers (see *INTRQ* registers on chapter 3.5). Purpose of the interrupt request is to re-initialize exhausted buffers by setting up the related DMA descriptors.

When a bit is set in one of the *INTRQ* register, the related *RCTST* and *XCTST* channel status registers shall be read. The *INTRQ* registers are read only type. Reading one

register will automatically reset all 8 bits. However, no interrupt can be missed, because the setting of a bit arriving during a CPU read cycle is delayed and therefore, the register reset after read will not apply to this bit.

The INTERRUPT REQUEST output (pin#67) will be true if at least one bit of any one of the eight *INTRQ* is set.

A flow chart of the interrupt routine is presented on figure 13.

# **3.0 Register Definitions**

All the control registers data are stored into the 29C94 internal RAM, which mapping is shown on table 2. As previously described in FUNCTIONAL

DESCRIPTION, starting on chapter 1.0, one can distinguished two kinds of control registers ; Global registers and context registers.

# Organization and definition

### 3.1. Global Registers

Control of global operating mode requires fourteen 8-bit registers. Only six of them, on addresses  $1000_{H}$ - $1001_{H}$ - $1002_{H}$ - $1003_{H}$ - $100C_{H}$ - $100D_{H}$ , are eventually used to specify operating mode. The other eight are split into two stacks of four 8-bit registers, on

addresses  $1004_{H}$ - $1005_{H}$ - $1006_{H}$ - $1007_{H}$  and  $1008_{H}$ - $1009_{H}$ - $100A_{H}$ - $100B_{H}$ , and are used to assert interrupt requests upon buffers switching. Register names and addresses, register status after reset and bit mnemonics are shown below, table 4.

| Registe  | er                  |       |       |       | MNEM  | ONICS |       |       |       | Reset             |

|----------|---------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------|

| Name     | Addr.               | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | State             |

| MODE     | 1000 <sub>H</sub>   | LB    | DXC1  | DXC0  | DPR8  | DPX8  | DC    | T1    | MSTR  | 00 <sub>H</sub>   |

| ROFFSET  | $1001_{\mathrm{H}}$ | DPR7  | DPR6  | DPR5  | DPR4  | DPR3  | DPR2  | DPR1  | DPR0  | $00_{\rm H}$      |

| XOFFSET  | 1002 <sub>H</sub>   | DPX7  | DPX6  | DPX5  | DPX4  | DPX3  | DPX2  | DPX1  | DPX0  | 00 <sub>H</sub>   |

| GLOBINH  | 1003 <sub>H</sub>   | NA    | GINH  | 00 <sub>H</sub>   |

|          | 1004 <sub>H</sub>   | ITX7  | ITX6  | ITX5  | ITX4  | ITX3  | ITX2  | ITX1  | ITX0  | 00 <sub>H</sub>   |

| XINTRQ   | $1005_{\mathrm{H}}$ | ITX15 | ITX14 | ITX13 | ITX12 | ITX11 | ITX10 | ITX9  | ITX8  | 00 <sub>H</sub>   |

|          | 1006 <sub>H</sub>   | ITX23 | ITX22 | ITX21 | ITX20 | ITX19 | ITX18 | ITX17 | ITX16 | 00 <sub>H</sub>   |

|          | $1007_{\mathrm{H}}$ | ITX31 | ITX30 | ITX29 | ITX28 | ITX27 | ITX26 | ITX25 | ITX24 | $00_{\rm H}$      |

|          | 1008 <sub>H</sub>   | ITR7  | ITR6  | ITR5  | ITR4  | ITR3  | ITR2  | ITR1  | ITR0  | $00_{\mathrm{H}}$ |

| RINTRQ   | 1009 <sub>H</sub>   | ITR15 | ITR14 | ITR13 | ITR12 | ITR11 | ITR10 | ITR9  | ITR8  | 00 <sub>H</sub>   |

|          | 100A <sub>H</sub>   | ITR23 | ITR22 | ITR21 | ITR20 | ITR19 | ITR18 | ITR17 | ITR16 | $00_{\rm H}$      |

|          | 100B <sub>H</sub>   | ITR31 | ITR30 | ITR29 | ITR28 | ITR27 | ITR26 | ITR25 | ITR24 | 00 <sub>H</sub>   |

| TESTREG0 | 100C <sub>H</sub>   | TST7  | TST6  | TST5  | TST4  | TST3  | TST2  | TST1  | TST0  | FF <sub>H</sub>   |

| TESTREG1 | 100D <sub>H</sub>   | NA    | TST8  | $01_{\rm H}$      |

| Table 4 : | Global | Operating | Mode | Control | <b>Registers.</b> |

|-----------|--------|-----------|------|---------|-------------------|

|-----------|--------|-----------|------|---------|-------------------|

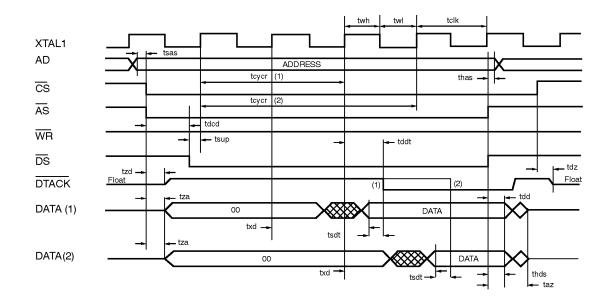

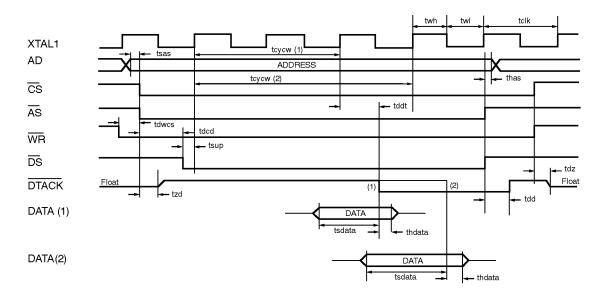

#### Read/Write into Global Registers

CPU intervention, read or write, into the global registers needs three XTAL1 periods. To either read or write into the registers, the host CPU drives a valid address on the system bus (AD 12;0), with CS = 0 (Chip Select). Data bytes are transferred to and from the 29C94 under the host CPU control according the truth table of table 5 below. Both write or read cycles end with a 29C94 acknowledgement that asserts DTACK=0 in MOTOROLA mode or DTACK=1 in INTEL mode.

Timing diagrams of the read and write operations are shown on chapters 6.3/6.4 (INTEL) and 7.3/7.4 (MOTOROLA).

| Table 5 : | Write/Read | operations on | <b>Global Contro</b> | l Registers |

|-----------|------------|---------------|----------------------|-------------|

| Table 5 . | //Itcau    | operations on | Olobal Contro        | I INCENSION |

|                                            | MOTOR | DLA Mode | INTEL Mode |      |     |

|--------------------------------------------|-------|----------|------------|------|-----|

| Signal Active Levels                       | Write | Read     | Write      | Read |     |

| MOTOROLA/INTEL MODE <sup>(1)</sup>         | MOT   | Vcc      | Vcc        | Gnd  | Gnd |

| ADDRESS LATCH ENABLE STROBE <sup>(2)</sup> | ALE   | Gnd      | Gnd        | 1    | 1   |

| CHIP SELECT.                               | CS    | 0        | 0          | 0    | 0   |

| ADDRESS STROBE                             | AS    | 0        | 0          | 1    | 0   |

| DATA STROBE                                | DS    | 0        | 0          | NA   | NA  |

| WRITE STROBE                               | WS    | 0        | 1          | 0    | 1   |

Notes :

The MOT pin (#50) must be definitely tied to VCC in MOTOROLA mode and to ground in INTEL mode.

The ALE pin (#29) should be tied to ground in MOTOROLA mode.

# **Global Register Descriptions & Bit Definitions**

## 3.2. MODE Register - Address 1000<sub>H</sub> -

The register specifies the global operating mode of the 29C94 according bit control listed in the truth table 6 below

#### Table 6 : Bit Functions in MODE Register

| Bit   |                | Bit level                     |                  |                                                                |                       |  |  |  |  |

|-------|----------------|-------------------------------|------------------|----------------------------------------------------------------|-----------------------|--|--|--|--|

| Mnemo | "1"            |                               |                  |                                                                | "0"                   |  |  |  |  |

| MSTR  | Master mode    |                               |                  |                                                                | Slave mode            |  |  |  |  |

| T1    | T1/DS1 opera   | ting mode                     |                  |                                                                | CEPT operating mode   |  |  |  |  |

| DC    | Double clock   |                               |                  |                                                                | Simple clock          |  |  |  |  |

| DPX8  | Transmit offse | Transmit offset extension bit |                  |                                                                |                       |  |  |  |  |

| DPR8  | Receive offset | t extension bit               |                  |                                                                |                       |  |  |  |  |

| DXC0  | DX output (pi  | n # 55) driving 1             | node programm    | ing                                                            |                       |  |  |  |  |

| DXC1  |                | DXC1                          | DXC0             |                                                                | DX output             |  |  |  |  |

|       |                | 0<br>0<br>1<br>1              | 0<br>1<br>0<br>1 | High impedance<br>Always driving<br>Open collector<br>Not used |                       |  |  |  |  |

| LB    | Loop back, fo  | r test purpose                |                  |                                                                | Normal operating mode |  |  |  |  |

When loop back mode is selected all transmit channels are looped back to their corresponding receive channels through the PCM HANDLER. In that operating mode the receive and transmit offset programming as well as byte alignment procedure must be as explained in the FRAME SYNC OFFSET chapter starting on chapter 2.1. Special attention should be devoted to,

- 1 Set-up the DMA descriptors for both transmit and receive channels on every single or hyper channel.

- 2 Program *RSPEED/XSPEED* registers of related channels with the same value.

- 3 Program *RMOD* register, the channel number and **ITVR** bit, on every single and hyperchannel, ending with hyperchannel head as explained on chapter 3.7.

- 4 Wait for all **ITVR** being set to "1" on every single and hyperchannel.

- 5 Program *XMOD* register, the channel number and **ITVR** bit, on every single and hyperchannel, ending with hyperchannel head.

After completion of this procedure, the device is fully ready for transmit/receive loop.

## 3.3. OFFSET Registers – ROFFSET at 1001<sub>H</sub>, XOFFSET at 1002<sub>H</sub> – TEST REGISTERS – TESTREGO at 100CH, TESTREG1 at 100DH –

OFFSET REGISTERS and TEST REGISTERS are working in conjunction. Binary count is used. The *TESTREG* specifies the number of time slot (one time slot=eight bit clock) to be used in the selected operating mode (24 T1/DS1, 32 CEPT).

Provided that the 9-bit word TST (8:0) contained in *TESTREGO* and *TESTREG1* registers is as shown in Table 7, then the PCM counters will count accordingly. Otherwise, the PCM counters will count by TST (8:0) + 1.

| MODE   | -                   | 7 Value<br>T (8;0)    | PCM Counters<br>Decimal Count |            |  |

|--------|---------------------|-----------------------|-------------------------------|------------|--|

|        | Single Clk          | Single Clk Double Clk |                               | Double Clk |  |

| CEPT   | 01111111            | 11111111              | 256                           | 512        |  |

| T1/DS1 | 011000000 111000001 |                       | 193 386                       |            |  |

#### Table 7 : PCM Counters and Test Registers programming.

**Master mode** : The 29C94 generates the FSX/FSR frame sync at 8 kHz by using the XCLK and RCLK bit clocks.

The width of FSX/FSR sync pulses is one XCLK/RCLK period. Pulses are triggered when the PCM bit counters reach the value programmed in the offset registers (DPR8 and DPX8 bits are only used in double clock mode).

The 29C94 includes two PCM counters, one for transmitting and one for receiving. The counters are incremented by XCLK (transmit) and RCLK (receive) and thus keep track of time slots and PCM frame sequence. The DPR8/DPX8 extension bit allows to count

up to 512, as necessary in double clock mode with a CEPT frame (for more information see technical note).

**Slave mode** : The FSR/FSX frame syncs are supplied to the 29C94. They are used to preset the PCM counters with the content of the offset registers. Counters presetting takes place *on falling edge of XCLK/RCLK with FSX/FSR high*. The frame sync pulse must be one bit clock period wide.

**Double clock** : This mode relates to GCI standard. For both XCLK and RCLK, two bit clock are used per single bit frame.

#### 3.4. GLOBINH Register – Address 1003<sub>H</sub> –

Applying a RESET to the 29C94 (see table 1 RESET logic levels) results in a global inhibit of the device.

After reset the HDLC PROCESSOR is idle and DX output is in high impedance state. The global control registers status is shown on table 4 immediately after reset. However, reset applies only to the global registers and not to the context ones. Caution must be exercized for a proper initialisation of the whole device.

#### **3.5. XINTRQ** – Address 1004<sub>H</sub> thru 1007<sub>H</sub> – **RINTRQ** – Address 1008<sub>H</sub> thru 100B<sub>H</sub> –

These two sets of registers are used to signal that a data frame completion and therefore a buffer switching, has occurred on a receive or transmit channel. Upon data frame completion, a bit is automatically set to "1" in the related register, at the location that points to the channel number. First, it is necessary to let GINH (bit 0 of GLOBINH register) be at low level for a least 2 full PCM frames with valid XCLK and RCLK. It is also mandatory to have the channels control registers set up by the host CPU before letting GINH be at logical "1". Not following this procedure would induce 29C94 erratic behaviour.

Any bit at "1" in the set of registers asserts the INTREQ output high (pin # 67), thus calling for the host CPU to read and memorize all eigth interrupt registers. The host will then read the status registers of the interrupting channel(s). The **XINTRQ/RINTRQ** registers are reset to zero when read by the cpu. Fig. 13 illustrates an interrupt routine.

# ΤΕΜΙΟ

#### Figure 13. Interrupt Routine.

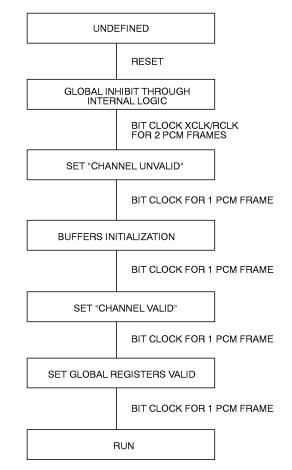

Figure 14. Exemple of initialization procedure.

# Initialization

Upon power-up the 29C94 must be resetted. This is performed by asserting the RESET signal for, at least, two PCM frame periods with valid XCLK and RCLK bit clock. All global registers are set in reset values as indicated in table 4. The 29C94 is then in slave, single clock CEPT operating mode. The whole chip is inhibited, and frame offset is zero. However, all the context registers are still in undefined states and should be set up by the host CPU as shown in the following flow chart. Literate explanations of the procedure may be found on chapter 3.7 where an hyperchannel setting procedure is described.

A diagram of an initialization procedure example in Figure 14.

# 3.6. Channel Context Register

Each PCM frame time slot has its own set of context registers. The registers are stacked into a double port RAM. An 8-bit wide port is used for CPU communication (Read/Write operations). The other port is 16-bit wide and is used in the successive operations of context restore-execute-save.

The 8-bit wide port to the outside world is sufficient because performances of the 29C94 is widely

self-supported, CPU intervention is not frequent. The 16-bit port is the gateway to the 29C94 internal bus. It needs to be wider because there are 128 bytes of context data to switch time slot after time slot.

The 32 CEPT receive contexts (24 in T1/DS1) are stored on decimal addresses 0H through 7FFH, while the transmit contexts are stored from 800H through FFFH (see table 2, internal RAM mapping).

# **Context Registers Description & Bit Definition**

Each time slot is associated with a set of receive and transmit context registers that define reciprocally the receive and transmit channel. Tables 8 and 9 thereafter, describe the details of receive and transmit context for time slot 0. These sets of registers are repeated for all 32 time slots as previously explained, that is to say a total of 64 single channels (32 receive + 32 transmit).

It should be noticed that the organization of the channel context is split in two parts. The first part, referred as the

HDLC descriptor, is related to transmit/receive data processing for that time slot. It contains various operating parameters and data which purposes are defined further on.

The other part of the context data is called the DMA descriptor; It contains word count, buffer address and DMA status. That second part of the channel context is replicated eight times, once per buffer, since for each channel is allocated eight chained buffers.

# Table 8 : Time Slot 0, Receive Context Registers.

|        |                                                                     |                    |             | MNE                              | MONICS            |               |              |        | Context                   | Register                  |

|--------|---------------------------------------------------------------------|--------------------|-------------|----------------------------------|-------------------|---------------|--------------|--------|---------------------------|---------------------------|

|        | bit 7                                                               | bit 6              | bit 5       | bit 4                            | bit 3             | bit 2         | bit 1        | bit 0  | Name                      | address                   |

|        | Channel Number (bit "log4" thru "log0") N.U <sup>(1)</sup> XPRT ITV |                    |             |                                  |                   |               |              |        | RMOD                      | 0000 <sub>H</sub>         |

| H<br>D |                                                                     |                    | RSPEED      | 0001 <sub>H</sub>                |                   |               |              |        |                           |                           |

| L<br>C | Cu                                                                  | rrent Buffer n     | umber       | umber FTR DMAD Data Frame Status |                   |               |              |        |                           | 0002 <sub>H</sub>         |

| D      | ITac                                                                | N.U <sup>(1)</sup> | N.U(1)      | Sta                              | ite Mac           |               | Bit count    |        | RSTAT2                    | 0003 <sub>H</sub>         |

| E<br>S |                                                                     |                    | Shift 3     | $0004_{\mathrm{H}}$              |                   |               |              |        |                           |                           |

| С      |                                                                     |                    |             | Shift                            | Register 2        |               |              |        | Shift 2                   | $0005_{\rm H}$            |

| R<br>I |                                                                     |                    |             | Shift                            | Register 1        |               |              |        | Shift 1                   | 0006 <sub>H</sub>         |

| P<br>T |                                                                     |                    |             | E                                | DATA              |               |              |        | FIFO                      | 0007 <sub>H</sub>         |

| O<br>R |                                                                     |                    | Fran        | ne check see                     | quence – low by   | yte –         |              |        | CRCL                      | 0008 <sub>H</sub>         |

|        |                                                                     |                    | Fram        | e check sec                      | uence – high b    | yte –         |              |        | CRCH                      | 0009 <sub>H</sub>         |

|        |                                                                     |                    |             |                                  | DMA De            | escriptor     |              |        | •                         |                           |

|        |                                                                     |                    | Buffe       | er 0. – Word                     | d count – low b   | yte –         |              |        | WCL <sub>0</sub>          | 000A <sub>H</sub>         |

|        |                                                                     |                    | Buffe       | er 0. – Word count – high byte – |                   |               |              |        | WCH <sub>0</sub>          | 000B <sub>H</sub>         |

|        |                                                                     |                    | Buffer 0. – | Current Ad                       | ldress pointer –  | low byte -    |              |        | ACTL <sub>0</sub>         | 000C <sub>H</sub>         |

|        |                                                                     |                    | Buffer 0. C | Current Add                      | lress pointer – h | nigh byte –   |              |        | ACTH <sub>0</sub>         | 000D <sub>H</sub>         |

|        | Lsyn                                                                | Ftr                | Tout        | Udf                              | Nba               | Abrt          | CRCe         | Done   | RCTST                     | 000E <sub>H</sub>         |

|        |                                                                     | Buffer 0.          |             |                                  |                   | Page Address  |              |        | SEGMT <sub>0</sub>        | 000F <sub>H</sub>         |

| D      | Buffer 1. Word count, Address pointer,                              |                    |             |                                  |                   |               |              |        |                           | 0010 <sub>H</sub><br>thru |

| M<br>A | Buffer 1 Page, Status                                               |                    |             |                                  |                   |               |              |        |                           | 0015 <sub>H</sub>         |

| D      | Buffer 2.                                                           |                    | Wo          | ord count                        |                   | Address point | 10.0         |        |                           | 0016 <sub>H</sub><br>thru |

| E<br>S | Buffer 2.                                                           |                    |             |                                  |                   | Address point | Page         | Status |                           | 001B <sub>H</sub>         |

| C<br>R | Buffer 3.                                                           |                    | Wo          | ord count                        | ·                 | A 11          |              |        |                           | 001C <sub>H</sub>         |

| Ι      | Buffer 3.                                                           |                    |             |                                  |                   | Address point | er,<br>Page  |        |                           | thru<br>0021 <sub>H</sub> |

| P<br>T | Buffer 4. Word count,                                               |                    |             |                                  |                   |               |              |        |                           | 0022 <sub>H</sub>         |

| O<br>R | Buffer 4.                                                           |                    |             |                                  |                   | Address point | ter,<br>Page | Status |                           | thru<br>0027 <sub>H</sub> |

|        | Buffer 5.                                                           |                    | Wo          | ord count                        |                   |               |              |        |                           | 0028 <sub>H</sub>         |

|        | Address pointer,<br>Buffer 5 Page, Status                           |                    |             |                                  |                   |               |              |        | thru<br>002D <sub>H</sub> |                           |

|        | Buffer 6.                                                           |                    | Wo          | ord count                        | ·                 |               |              |        |                           | 002E <sub>H</sub>         |

|        | Buffer 6.                                                           |                    |             |                                  |                   | Address point | ter,<br>Page | Status |                           | thru<br>0033 <sub>H</sub> |

|        | Buffer 7.                                                           |                    | Wo          | ord count                        |                   | Address       | tor          |        |                           | 0034 <sub>H</sub>         |

|        | Buffer 7.                                                           |                    |             |                                  |                   | Address point | ter,<br>Page | Status |                           | thru<br>0039 <sub>H</sub> |

Note : 1. N.U = Not Used.

#### Table 9 : Time Slot 0, Receive Context Registers.

|        |                                                       |                    |                    | MNE                              | MONICS             |                 |                |          | Context            | Register                                       |

|--------|-------------------------------------------------------|--------------------|--------------------|----------------------------------|--------------------|-----------------|----------------|----------|--------------------|------------------------------------------------|

|        | bit 7                                                 | bit 6              | bit 5              | bit 4                            | bit 3              | bit 2           | bit 1          | bit 0    | Name               | address                                        |

|        | Channel Number (bit "log4" thru "log0") FLG XPRT ITVX |                    |                    |                                  |                    |                 |                |          |                    | 0800 <sub>H</sub>                              |

| H<br>D | Rate adaptor – Fill Mask. (bit "XSP7" thru "RSP0")    |                    |                    |                                  |                    |                 |                |          |                    | 0801 <sub>H</sub>                              |

| L<br>C | Cu                                                    | rrent Buffer n     | umber              | FTR                              | DMAD               | Dat             | ta Frame Statu | 18       | XSTAT1             | 0802 <sub>H</sub>                              |

| D      | ITac                                                  | N.U <sup>(1)</sup> | Trai               | nsmit State                      | Mac                |                 | Bit count      |          | XSTAT2             | 0803 <sub>H</sub>                              |

| Е      |                                                       |                    |                    | Shift                            | Register           |                 |                |          | Shift 1            | 0804 <sub>H</sub>                              |

| S<br>C | N.U <sup>(1)</sup>                                    | FII                | FO CONTROL         |                                  | TAC                | G 2             | TAC            | G 1      | TAG                | 0805 <sub>H</sub>                              |

| R<br>I |                                                       |                    |                    | F                                | IFO 1              |                 |                |          | FIFO1              | 0806 <sub>H</sub>                              |

| P<br>T |                                                       |                    |                    | F                                | IFO 2              |                 |                |          | FIFO2              | 0807 <sub>H</sub>                              |

| O<br>R |                                                       |                    | Fran               | ne check see                     | quence – low by    | yte –           |                |          | CRCL               | 0808 <sub>H</sub>                              |

|        |                                                       |                    | Fram               | e check sec                      | uence – high b     | yte –           |                |          | CRCH               | 0809 <sub>H</sub>                              |